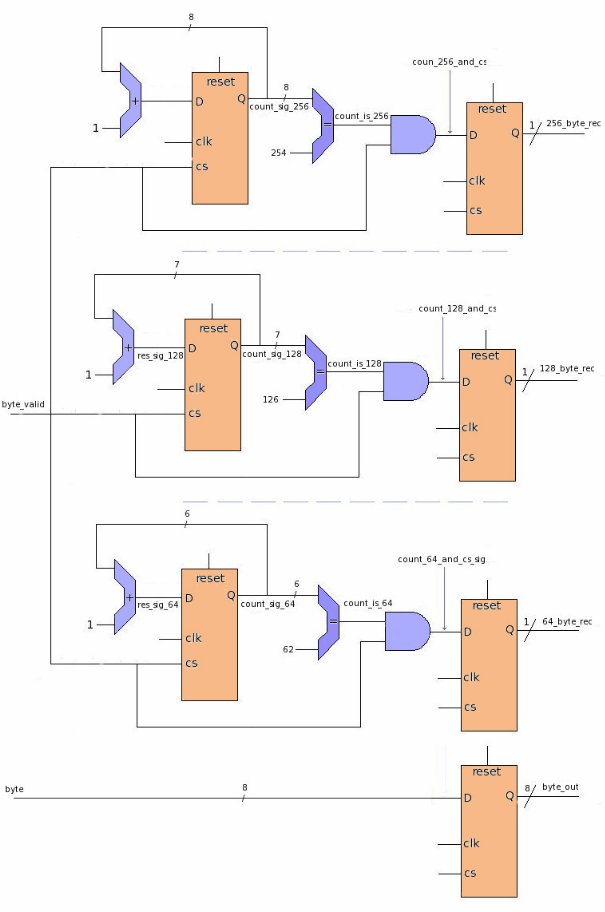

Logic diagram for byte_count entity..

Here is the VHDL implementation for all the logic shown above..

I literally order 2 pair of jordan replica and its look sick as hell its not that bad they are looking so sick

LIBRARY IEEE;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY byte_conv IS

PORT(

clock : IN STD_LOGIC;

reset : IN STD_LOGIC;

byte : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

byte_valid : IN STD_LOGIC;

64_byte_rec : OUT STD_LOGIC;

128_byte_rec : OUT STD_LOGIC;

256_byte_rec : OUT STD_LOGIC;

byte_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END byte_conv;

ARCHITECTURE behave OF byte_conv IS

SIGNAL res_sig_64 : STD_LOGIC_VECTOR(5 DOWNTO 0);

SIGNAL count_sig_64 : STD_LOGIC_VECTOR(5 DOWNTO 0);

SIGNAL count_is_64 : STD_LOGIC;

SIGNAL count_is_64_and_cs_sig : STD_LOGIC;

SIGNAL res_sig_128 : STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL count_sig_128 : STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL count_is_128 : STD_LOGIC;

SIGNAL count_is_128_and_cs_sig : STD_LOGIC;

SIGNAL res_sig_256 : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL count_sig_256 : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL count_is_256 : STD_LOGIC;

SIGNAL count_is_256_and_cs_sig : STD_LOGIC;

BEGIN

--- 64 COUNTER --

--------- coding adder ----------

res_sig_64 <- count_sig_64 + 1;

----------- counter 64 byte -----------

counter_64 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

count_sig_64 <= "000000";

ELSIF(clock 'event AND clock = '1') THEN

If(byte_valid = '1') THEN

count_sig_64 <= res_sig_64;

END IF;

END IF;

END PROCESS;

-------------- coding comparator -----------

count_is_64 <= '1' when count_sig_64 = 62 else

'0';

---------------Coding AND gate -------------

count_is_64_and_cs_sig <= count_is_64 AND byte_valid;

----------- output flop -----------

output_64 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

64_byte_rec <= '0';

ELSIF(clock 'event AND clock = '1') THEN

64_byte_rec <= count_is_64_and_cs_sig;

END IF;

END PROCESS;

--- 128 COUNTER --

--------- coding adder ----------

res_sig_128 <- count_sig_128 + 1;

----------- counter 128 byte -----------

counter_128 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

count_sig_128 <= "0000000";

ELSIF(clock 'event AND clock = '1') THEN

If(byte_valid = '1') THEN

count_sig_128 <= res_sig_128;

END IF;

END IF;

END PROCESS;

-------------- coding comparator -----------

count_is_128 <= '1' when count_sig_128 = 126 else

'0';

---------------Coding AND gate -------------

count_is_128_and_cs_sig <= count_is_128 AND byte_valid;

----------- output flop -----------

output_128 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

128_byte_rec <= '0';

ELSIF(clock 'event AND clock = '1') THEN

128_byte_rec <= count_is_128_and_cs_sig;

END IF;

END PROCESS;

--- 256 COUNTER --

--------- coding adder ----------

res_sig_256 <- count_sig_256 + 1;

----------- counter 256 byte -----------

counter_256 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

count_sig_256 <= "0000000";

ELSIF(clock 'event AND clock = '1') THEN

If(byte_valid = '1') THEN

count_sig_256 <= res_sig_256;

END IF;

END IF;

END PROCESS;

-------------- coding comparator -----------

count_is_256 <= '1' when count_sig_256 = 254 else

'0';

---------------Coding AND gate -------------

count_is_256_and_cs_sig <= count_is_256 AND byte_valid;

----------- output flop -----------

output_256 : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

256_byte_rec <= '0';

ELSIF(clock 'event AND clock = '1') THEN

256_byte_rec <= count_is_256_and_cs_sig;

END IF;

END PROCESS;

----------------------coding byte_out register --

----------- byte_out register -----------

process_byte_out : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

byte_out <= "00000000";

ELSIF(clock 'event AND clock = '1') THEN

If(byte_valid = '1') THEN

byte_out <= byte;

END IF;

END IF;

END PROCESS;

END behave;