Specification of this entity is already very simple, it has to just keep receiving the bits for which bit_valid = '1'. As 8 bits (byte) gets accumulated, generate a pulse indicating that one byte is ready on the output.. that's all..

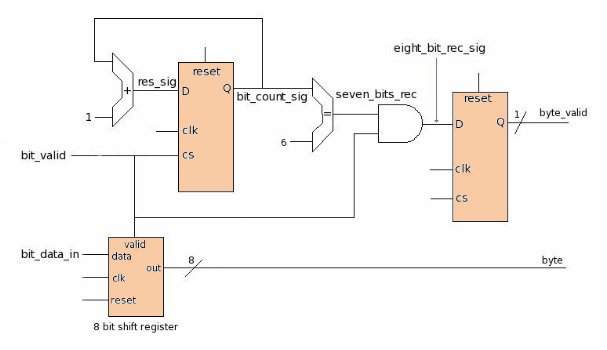

Below is the logic diagram implementation shown...

Here is the VHDL implementation for all the logic shown above..

LIBRARY IEEE;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY byte_conv IS

PORT(

clock : IN STD_LOGIC;

reset : IN STD_LOGIC;

bit_data_in : IN STD_LOGIC;

bit_valid : IN STD_LOGIC;

byte : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

byte_valid : OUT STD_LOGIC

);

END byte_conv;

ARCHITECTURE behave OF byte_conv IS

SIGNAL res_sig : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL bit_count_sig : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL seven_bit_rec : STD_LOGIC;

SIGNAL eight_bit_rec_sig : STD_LOGIC;

SIGNAL byte_out_sig : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

-----------Coding shift-register -----------

shift_register : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

byte_out_sig <= "00000000";

ELSIF(clock 'event AND clock = '1') THEN

If(bit_valid = '1') THEN

byte_out_sig(6 DOWNTO 0) < byte_out_sig(7 DOWNTO 1);

byte_out_sig(7) <= bit_data_in;

END IF;

END IF;

END PROCESS;

----------- Coding Counter -----------------

res_sig <= bit_count_sig + 1;

bit_counter_process : PROCESS(clock , reset)

BEGIN

IF (reset = '0') THEN

bit_count_sig <= "000";

ELSIF( clock 'event AND clock = '1') THEN

IF(bit_valid = '1') THEN

bit_count_sig <= res_sig;

END If;

END IF;

END PROCESS;

-------------- coding comparator -----------

seven_bit_rec <= '1' when bit_count_sig = "110" else

'0';

---------------Coding AND gate -------------

eight_bit_rec <= seven_bit_rec AND bit_valid;

---------------Coding output flip-flop for byte_valid -----

byte_valid_gen_flop : PROCESS(clock , reset)

BEGIN

If(reset = '0') THEN

byte_valid <= '0';

ELSIF(clock 'event AND clock = '1') THEN

byte_valid <= eight_bit_rec_sig;

END IF;

END PROCESS;

----------- byte out -------

byte_out <= byte_out_sig;

END behave;