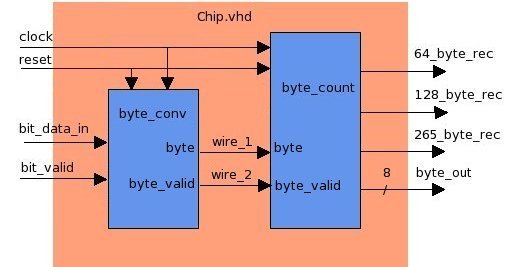

Here, both the entities (byte_conv, and byte_count) are instantiated and connected using wire_1 and wire_2. Signal wire_1 connects byte, and wire_2 connects byte_valid between two instances. Required outputs are routed to the top (chip.vhd).

1) LIBRARY IEEE;

2) USE ieee.std_logic_1164.ALL;

3) USE ieee.std_logic_arith.ALL;

4) USE ieee.std_logic_unsigned.ALL;

5)

6) ENTITY chip IS

7) PORT(

8) clock : IN STD_LOGIC;

9) reset : IN STD_LOGIC;

10) bit_data_in : IN STD_LOGIC;

11) bit_valid : IN STD_LOGIC;

12) 64_byte_rec : OUT STD_LOGIC;

13) 128_byte_rec : OUT STD_LOGIC;

14) 256_byte_rec : OUT STD_LOGIC;

15) byte_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

16) );

17)

18) END chip;

19)

20) ARCHITECTURE struct OF chip IS

21)

22) COMPONENT byte_conv

23) PORT (

24) clock : IN STD_LOGIC;

25) reset : IN STD_LOGIC;

26) bit_data_in : IN STD_LOGIC;

27) bit_valid : IN STD_LOGIC;

28) byte : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

29) byte_valid : OUT STD_LOGIC

30) );

31) END COMPONENT;

32)

33) COMPONENT byte_count

34) PORT (

35) clock : IN STD_LOGIC;

36) reset : IN STD_LOGIC;

37) byte : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

38) byte_valid : IN STD_LOGIC;

39) 64_byte_rec : OUT STD_LOGIC;

40) 128_byte_rec : OUT STD_LOGIC;

41) 256_byte_rec : OUT STD_LOGIC;

42) byte_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

43)

44) );

45) END COMPONENT;

46)

47) SIGNAL wire_1 : STD_LOGIC_VECTOR(7 DOWNTO 0);

48) SIGNAL wire_2 : STD_LOGIC;

49)

50) BEGIN

51)

52) byte_conv_instance : byte_conv

53) PORT MAP (

54) clock => clock,

55) reset => reset,

56) bit_data_in => bit_data_in,

57) bit_valid => bit_valid,

58) byte => wire_1,

59) byte_valid => wire_2

60) );

61)

62) byte_count_instance : byte_count

63) PORT MAP (

64) clock => clock,

65) reset => reset,

66) byte => wire_1,

67) byte_valid => wire_2,

68) 64_byte_rec => 64_byte_rec,

69) 128_byte_rec => 128_byte_rec,

70) 256_byte_rec => 256_byte_rec,

71) byte_out => byte_out

72) );

73)

74) END struct;

|