Lets modify our SR Flip-flop and provide a clock enable. This means that the output will change only when clock is '1', otherwise all inputs will be ignored. Note that this is leveled enable, i.e the input can change flip-flop's output only while the clock is '1'. While the clock is '0', all the inputs will be ignored.

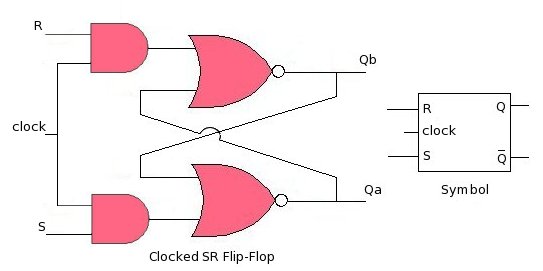

Small modification done in S-R flip-flop to provide clock enable is shown below...

Behavior of clocked flip-flop's is shown in the table below.

| S | R | Qa(t) | Qa (t + 1) |

| 0 | 0 | 0 -> | 0 |

| 0 | 1 | 0 -> | 1 |

| 1 | 0 | 0 -> | 1 |

| 1 | 1 | 0 -> | Invalid |

| 0 | 0 | 1 -> | 1 |

| 0 | 1 | 1 -> | 0 |

| 1 | 0 | 1 -> | 1 |

| 1 | 1 | 1 -> | Invalid |

Note that Qa(t) is current output at Qa, and Qa(t + 1) will be next output. The flipflop will switch from Qa(t) to Qa(t + 1) if the inputs (S & R) are feed as shown in the table. Also note that clock is also required to enable flip-flop otherwise all the inputs will be ignored. "INVALID" means for these inputs flip-flop's output will be unpredictable, hence these are invalid.